Arhitectura MIPS

Arhitectura MIPS ( English M icroprocessor fără a i nterlocked p ipeline s zi , germană ca „microprocesor , fără etape de conducte împăturite“) este un set de instrucțiuni de arhitectură în RISC stil, care din 1981 de John L. Hennessy si colegii sai de la Universitatea Stanford a fost dezvoltat . Dezvoltarea ulterioară a avut loc din 1984 la noua companie înființată MIPS Computer Systems Inc., ulterior MIPS Technologies , și astăzi aparține companiei americane de tehnologie Wave Computingcu sediul în Silicon Valley .

MIPS a fost inițial o arhitectură pe 32 de biți, extinderea pe 64 de biți a urmat în 1991 și a fost introdusă cu R4000. Multe arhitecturi RISC din acest timp s-au influențat reciproc, inclusiv Sun SPARC , procesorul Alpha al DEC sau PA-RISC al lui Hewlett-Packard . Arhitectura MIPS utilizează modelul de executare a registrului / registrului.

Din februarie 2013, arhitectura MIPS a fost dezvoltată și comercializată în continuare de compania britanică Imagination Technologies . În 2017, divizia MIPS, împreună cu divizia PowerVR , a fost vândută companiei chineze de investiții Canyon Bridge Capital Partners și a fost deținută recent de Tallwood Venture Capital . Din iunie 2018, arhitectura MIPS este una din 2010, fondată pe start-up-urile specializate AI Wave Computing, care, odată cu achiziționarea dezvoltării AI și Deep Learning, ar avansa în continuare prin combinarea ambelor tehnologii. MIPS Open Initiative a fost lansată la sfârșitul anului 2018 și s-a anunțat că arhitectura MIPS va fi plasată sub o licență open source la începutul anului 2019 .

utilizare

Procesoarele MIPS provin de la Silicon Graphics în Unix - stații de lucru (de ex. SGI Indigo ) și servere Unix (cum ar fi SGI. Origin2000 ) utilizate. În trecut, alți producători de stații de lucru precum B. echipamentele Digital Equipment Corporation (DEC) cu procesoare MIPS, deci z. B. familia DECstation (2100, 3100, 5000) și sistemul DEC din sistemul de operare Ultrix . Siemens și SNI și-au echipat serverele din seria RM cu procesoare MIPS din familiile R4000, R5000 și R10000, Sun a folosit procesoare din familia R5000 în mai multe modele de servere din seria Cobalt Qube și RaQ. Au existat încercări de accelerare a procesoarelor MIPS cu ajutorul tehnologiei ECL . Pentru aceasta a fost folosit tipul R6000, în cele din urmă o versiune ECL a R3000. Acest tip de procesor a fost utilizat în computerele de tip CDC 4680 de la Control Data Corporation .

La începutul anilor 1990, MIPS Computer Systems Inc. a început să acorde licență proiectelor sale de microprocesor unor terțe părți . De la mijlocul anilor 1990, arhitectura MIPS și-a găsit drumul în consolele de jocuri video Nintendo 64 (1996), PlayStation (1994), PlayStation 2 (2000) și PlayStation Portable (2004).

CPU-urile cu arhitectură MIPS sunt încă deseori utilizate în construcția de ex. Ca routere de rețea , sisteme de navigație auto , receptoare digitale , set-top box-uri și camere digitale SLR încorporate . Utilizarea nucleelor procesorului bazate pe MIPS în cadrul acestor clase de dispozitive are loc în contextul sistemelor cu un singur cip (SoC). Imagination Technologies oferă producătorilor atât nuclee IP gata făcute, cât și o licență de arhitectură.

Institutul de Tehnologie de Calcul (ICT) al Academiei Chineze de Științe a obținut o licență de arhitectură pentru dezvoltarea procesorului Loongson compatibil MIPS în 2009. Modelul Loongson 3B formează baza microprocesorului pentru supercomputerul chinez Dawning 6000.

funcţie

O instrucțiune în aceste procesoare este procesată în mai multe etape într-o conductă , astfel încât mai multe instrucțiuni în diferite etape de procesare (de exemplu, instrucțiuni de preluare, decodare a instrucțiunilor și preluarea operanzilor, executarea instrucțiunilor cu operanzi, citirea sau scrierea memoriei principale și scrierea înapoi a rezultatului) în procesor în același timp poate. Dacă o comandă ulterioară se bazează pe rezultatul uneia anterioare, este posibil ca comanda ulterioară să fie oprită până când rezultatul este disponibil. Acest lucru se realizează de obicei prin încuietori („tarabe”). O altă opțiune pentru procesarea unor astfel de obstacole de date este așa-numita „redirecționare”, în care rezultatele calculului necesare pentru următoarea instrucțiune sunt trecute la următoarea instrucțiune imediat după calcul, în loc să preia valoarea dintr-un registru în următorul ciclu posibil.

Arhitectura MIPS dispune de astfel de blocări și necesită programatorului de limbaj de asamblare sau compilatorului să ia măsurile adecvate, cum ar fi re-sortarea sau inserarea operațiunilor zero (NOP). Acest lucru permite arhitecturii să fie simplă. S-a arătat, totuși, că codul mașinii a fost umflat de comenzile NOP pentru a fi introdus în așa fel încât rata de accesare în memoria cache a comenzilor introdusă ulterior a fost redusă. La rândul său, acest lucru a dus la pierderi de performanță, care ar trebui de fapt evitate prin renunțarea inițială la blocare. Prin urmare, au fost implementate măsuri în versiunile MIPS ulterioare, care permit programului să ruleze fără a lua în considerare etapele conductei. Abrevierea „MIPS” și-a pierdut de atunci sensul real.

Un alt mecanism utilizat pentru a accelera arhitectura MIPS este ceea ce este cunoscut sub numele de superpipelining. Spre deosebire de arhitecturile spațiale paralele (de exemplu, procesoarele VLIW ), un paralelism temporal al procesării comenzilor se realizează aici prin împărțirea conductei de comandă în mai multe etape. Aceasta creează o subdiviziune mai bună a liniei de asamblare. Etapele conductei au un timp de răspuns mai scurt în acest mod și, prin urmare, rata de ceas poate fi mărită. Superpipelining-ul a fost implementat pentru prima dată în procesoarele MIPS-R4000.

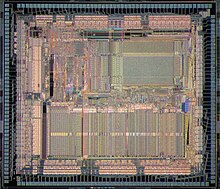

Procesoare MIPS

| model | Frecvența în MHz |

an | Proces de fabricație în µm |

Tranzistoare în milioane |

Dimensiunea în mm² |

Pini IO | Putere în W |

Tensiunea în V |

Dcache în KiB |

Icache în KiB |

Scache în MiB |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R2000 | 8.3 ... 16.7 | 1985 | 2.0 | 0,11 | 80 | ? | ? | ? | 32 | 64 | - |

| R2000A | 12,5 ... 16,7 | 1988 | 2.0 | 0,11 | 80 | ? | ? | ? | 32 | 64 | - |

| R3000 | 20 ... 33 | 1988 | 1.2 | 0,11 | 66.12 | 145 | Al 4-lea | ? | 64 | 64 | - |

| R3000A | 25 ... 40 | 1989 | 1.2 | 0,11 | 66.12 | 145 | Al 4-lea | ? | 64 | 64 | - |

| R4000 | 100 | 1991 | 1-0.8 | 1,35 | 213 | 179 | 15 | 5 | A 8-a | A 8-a | 1 |

| R4300 | 93,75 | 1996 | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| R4400 | 150 ... 250 | 1992 | 0,6 | 2.3 | 186 | 179 | 15 | 5 | 16 | 16 | 1 |

| R4600 | 133 | 1994 | 0,64 | 2.2 | 77 | 179 | 4.6 | 5 | 16 | 16 | 0,5 |

| R5000 | 150 ... 200 | 1996 | 0,35 | 3.7 | 84 | 223 | 10 | 3.3 | 32 | 32 | 1 |

| R7000 | 250 ... 600 | 2000 | 0,13 | ? | ? | 304 | 2-3 | 3.3 (io) / 1.2 (int) | 16 | 16 | 0,25 |

| R8000 | 75 ... 90 | 1994 | 0,5 | 2.6 | 299 | 591 | 30 | 3.3 | 16 | 16 | 1 ... 8 |

| R10000 | 150 ... 270 | 1995 | 0,35 | 6.8 | 299 | 599 | 30 | 3.3 | 32 | 32 | 0,5 ... 16 |

| R12000 | 300 ... 400 | 1998 | 0,18-0,25 | 6.9 | 204 | 600 | 20 | 2.3 | 32 | 32 | 0,5 ... 16 |

| R14000 | 500 ... 600 | 2001 | 0,13 | 7.2 | 204 | 527 | 17 | 1.5 | 32 | 32 | 0,5 ... 16 |

| R16000 | 700 | 2002 | 0,11 | ? | ? | ? | 20 | 1.5 | 32 | 32 | 0,5 ... 16 |

| R16000A | 800 ... 1000 | 2004 | 0,11 | ? | ? | ? | ? | 1.5 | 32 | 32 | 0,5 ... 16 |

Emulatoare

- QtSpim - cea mai recentă versiune a Spim, interfață cu utilizatorul pe mai multe platforme.

- EduMIPS64

- GXemul

- MARS (MIPS Assembler and Runtime Simulator) este un emulator MIPS32 scris în Java la Universitatea de Stat din Missouri .

- OVPsim

- QEMU

- Simics

- SPIM

- JPCSP este un emulator MIPS R4000 (Allegrex) bazat pe limbajul de programare Java, care emulează în principal software-ul PSP .

- Unicorn este un emulator bazat pe QEMU care oferă interfețe pentru multe limbaje moderne de programare (inclusiv C, Python și Java).

Vezi si

literatură

- David A. Patterson, John L. Hennessy: Organizarea și proiectarea computerelor, interfața hardware / software . Ediția a IV-a. Morgan Kaufmann Publishers, San Francisco 2008, ISBN 0-12-374493-8 .

- John L. Hennessy, David A. Patterson: Arhitectura computerelor - O abordare cantitativă . 3. Ediție. Morgan Kaufmann Publishers, San Francisco 2003, ISBN 1-55860-724-2 .

Link-uri web

- Procesoare MIPS: imagini și descrieri pe cpu-collection.de

- MIPS Technologies, Inc.

- Patterson și Hennessy - Anexa A (PDF, 483 KiB)

Dovezi individuale

- ^ Prezentare generală a arhitecturii MIPS. Adus pe 27 mai 2012 .

- ↑ Benjamin Kraft: Imagination Technologies vândute grupului de investitori chinezi. În: Heise online . 24 septembrie 2017 . Adus la 17 iunie 2018.

- ↑ Bernd Mewes: Wave Computing, specialist în AI, cumpără MIPS. În: Heise online . 16 iunie 2018 . Adus la 17 iunie 2018.

- ↑ Alexandra Kleijn: Arhitectura procesorului: MIPS devine open source. În: Heise online . 18 decembrie 2018 . Adus la 18 decembrie 2018.; Citat: „Arhitectura procesorului MIPS va intra sub licență open source la începutul anului 2019 și va fi dezvoltată în continuare ca parte a inițiativei MIPS Open”.

- ↑ Andreas Stiller: Procesor Whisper - From MIPS and MIPS In: c't - magazine for computer technology , 9 octombrie 2010.

- ↑ QtSpim

- ↑ courses.missouristate.edu MARS (MIPS Assembler and Runtime Simulator)

- ↑ Unicorn: Unicorn - Ultimul emulator CPU. Adus pe 12 septembrie 2017 .